# Semiconductor Solutions for 48V High Power Inverter

# Alternatives to Bare Die Modules

Eric Schütte Infineon Technologies AG

# Agenda

| 1 | High Power Inverters          |

|---|-------------------------------|

| 2 | Leadless SMD Packages         |

| 3 | Bare Dies and MOSFET Modules  |

| 4 | Innovative Packaging Concepts |

| 5 | Chip Embedding                |

| 6 | Summary and Outlook           |

# Agenda

| 1 | High Power Inverters          |

|---|-------------------------------|

| 2 | Leadless SMD Packages         |

| 3 | Bare Dies and MOSFET Modules  |

| 4 | Innovative Packaging Concepts |

| 5 | Chip Embedding                |

| 6 | Summary and Outlook           |

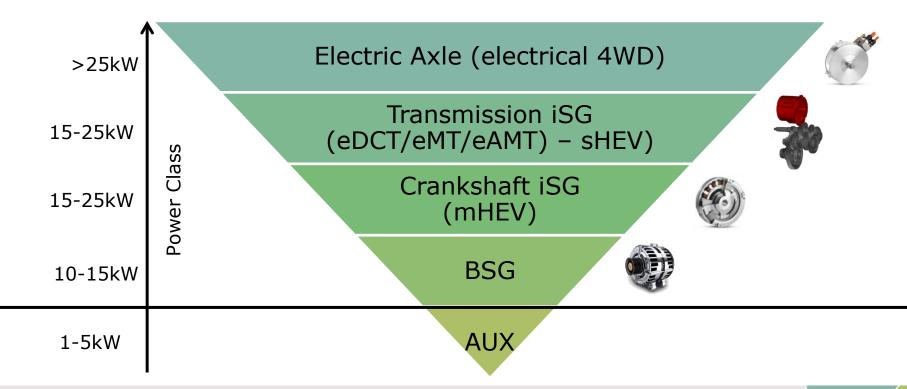

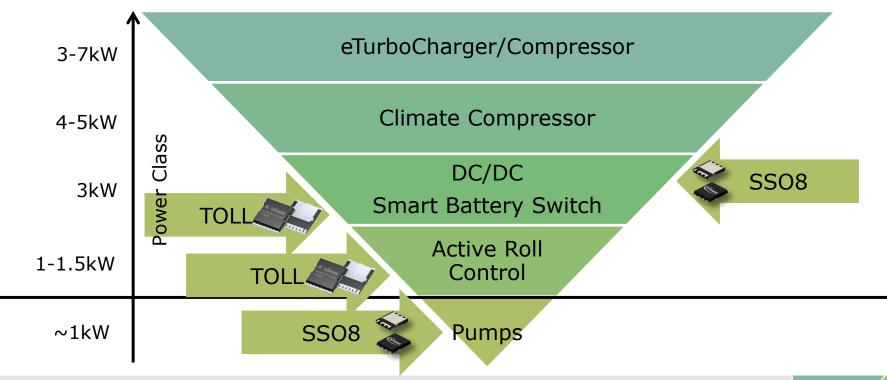

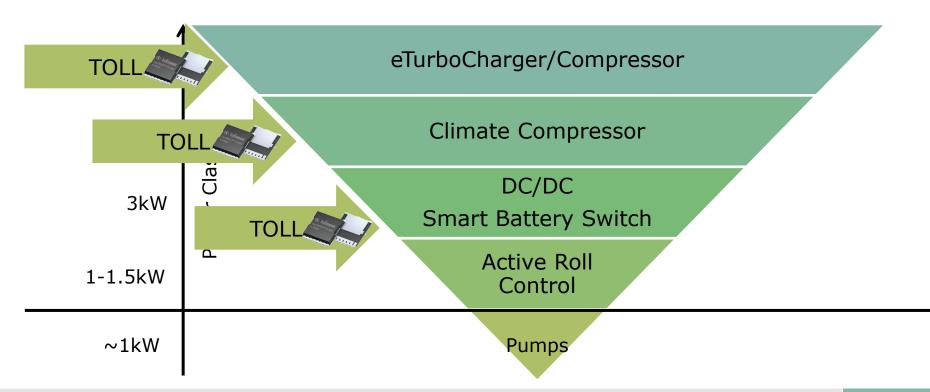

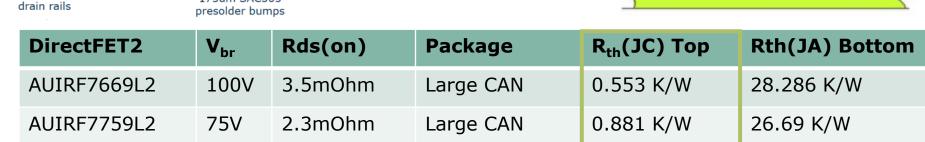

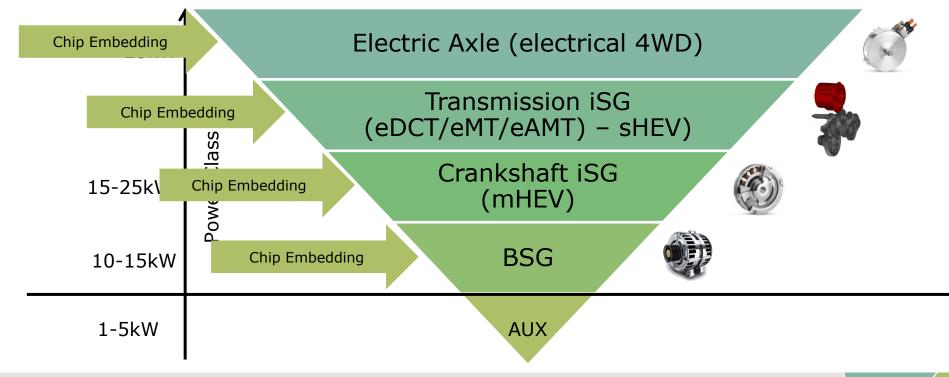

## High Power Inverters µHybridization

> Electrification and Hybridization

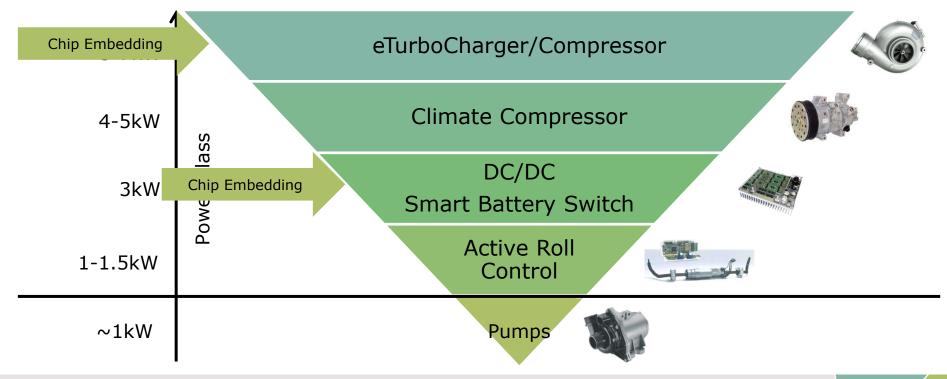

## High Power Inverters Auxiliary Drives

Copyright © Infineon Technologies AG 2017. All rights reserved.

# Agenda

| 1 | High Power Inverters          |

|---|-------------------------------|

| 2 | Leadless SMD Packages         |

| 3 | Bare Dies and MOSFET Modules  |

| 4 | Innovative Packaging Concepts |

| 5 | Chip Embedding                |

| 6 | Summary and Outlook           |

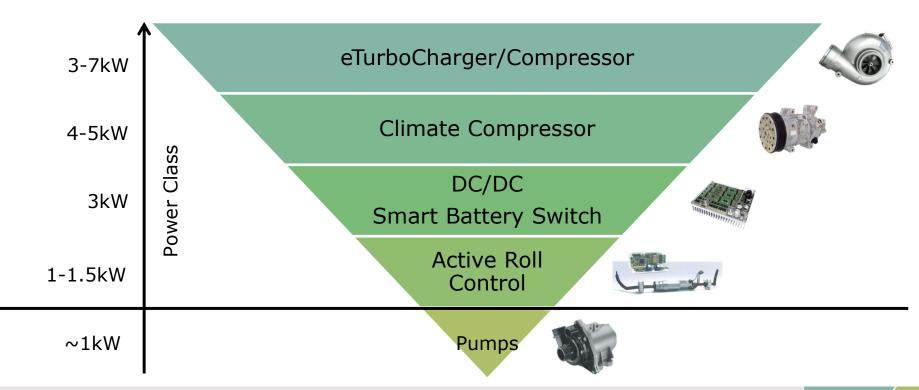

## Leadless MOSFETs OptiMOS<sup>™</sup>5 80V/100V Trench Technology

### **Best in Class Rdson**

- Leading R<sub>DSon</sub> performance down to 1.2mOhm (released)

- Low conduction losses

- Area reduction facilitates smaller packages

#### 1. Applicable to normal level 2017-09-18 restricted

### **EMC Improvement**

- Reduced Ciss & Coss

- Improved switching behavior

- Improved EMC behavior due to technology improvements

## Innovative package interconnect

- New top-side copper-clip contact technology

- Lower thermal resistance

- Lower package resistance

- Smaller package e.g. Achieved a footprint 1/6<sup>th</sup> the size of a DPAK for equivalent R<sub>DSon</sub>

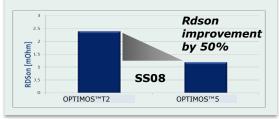

## Back End Technology Portfolio and Roadmap

sTOLL registered at JEDEC

#### 2017-10-12

Copyright © Infineon Technologies AG 2017. All rights reserved.

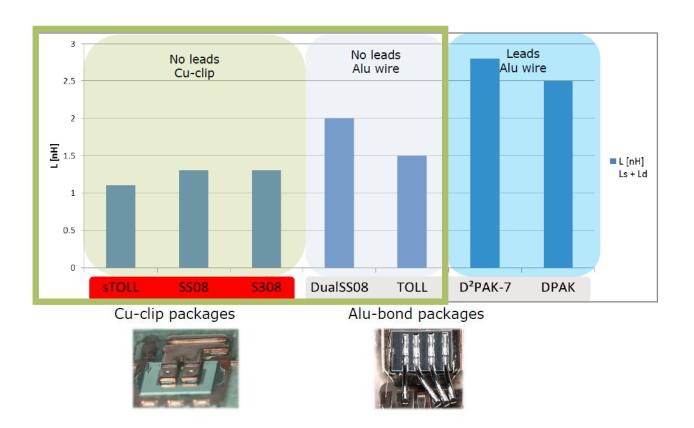

## Leadless MOSFETs Interconnect Technology

- Cu-Clip Packages

offer Lowest Package

Resistance &

Inductance

- > Best EMI Behavior

- Lowest Voltage

Overshoots

## Robustness of Leadless Packages IOL Test

## **IOL**=**I**ntermittent **O**perating Livetime ("Power Cycling")

| Testing conditions acc. AEC Q101                                                                                                     |                                                                                          |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|

| Start Temperature                                                                                                                    | 20°C                                                                                     |  |  |

| Temperature rise during cycles                                                                                                       | ΔΤ=100Κ                                                                                  |  |  |

| Current                                                                                                                              | Applied to the bodydiode for a few seconds to heat up the chip to the target temperature |  |  |

| Number of tested devices                                                                                                             | 77                                                                                       |  |  |

| Number of power cycles                                                                                                               | 15.000 with no failures                                                                  |  |  |

| Premisses                                                                                                                            |                                                                                          |  |  |

| <ul> <li>cooling down the device needs approximately 3 minutes</li> <li>a parameter drift of 20% is considered as failure</li> </ul> |                                                                                          |  |  |

|                                                                                                                                      |                                                                                          |  |  |

#### Measured parameters

All standard parameters according to datasheet: Leakage currents,  $V_{BRDSS}$ ,  $V_{GSth}$ ,  $R_{DS(on)}$  etc.

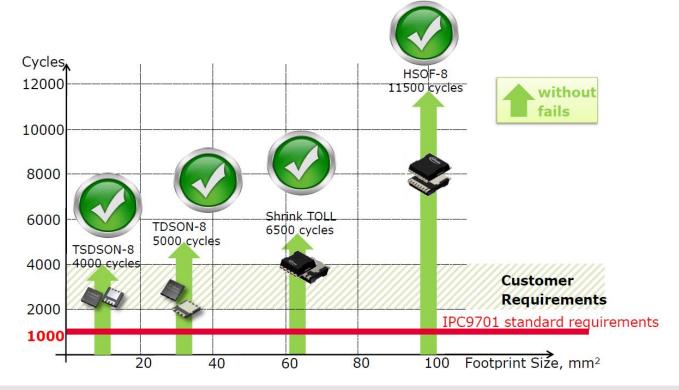

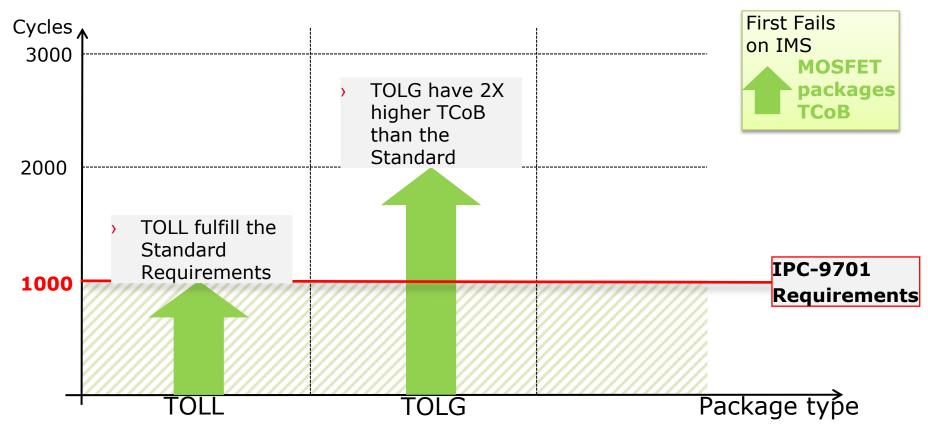

## Robustness of Leadless Packages Beyond IPC-9701

> Enhanced TCoB Performance

## 80V & 100V MOSFET Portfolio with Leadless Packages

|                       | PQFN 5x6<br>(TDSON) | PQFN5x6<br>(TDSON) | SSO8<br>(TDSON)  | SSO8<br>(TDSON)   | TOLL<br>(H-SOF)  | TOLL<br>(H-SOF)   | DirectFET2<br>(WDSON) |

|-----------------------|---------------------|--------------------|------------------|-------------------|------------------|-------------------|-----------------------|

|                       |                     |                    |                  |                   |                  |                   | TSR                   |

| Foot-Print            | 5x6mm               | 5x6mm              | 5x6mm            | 5x6mm             | 10x12mm          | 10x12mm           | 7x9mm <sup>2</sup>    |

| I-Package             | 100A                | 100A               | 100A             | 100A              | 300A             | 300A              | 88A                   |

| Released              | Gen 10.7<br>75V     | Gen 10.7<br>100V   | OptiMOS™5<br>80V | OptiMOS™5<br>100V | OptiMOS™5<br>80V | OptiMOS™5<br>100V | Gen10.7<br>100V       |

| R <sub>DSon</sub> BiC | 8.5mΩ               | 14.5mΩ             | 3.1mOhm          | 4mOhm             | 1.2mΩ            | 1.5mOhm           | 2.8mΩ                 |

- > Suitable for standard FR4 PCBs

- > High Reliability during TCoB and IOL Tests

- Preliminary Information. Subject to change.

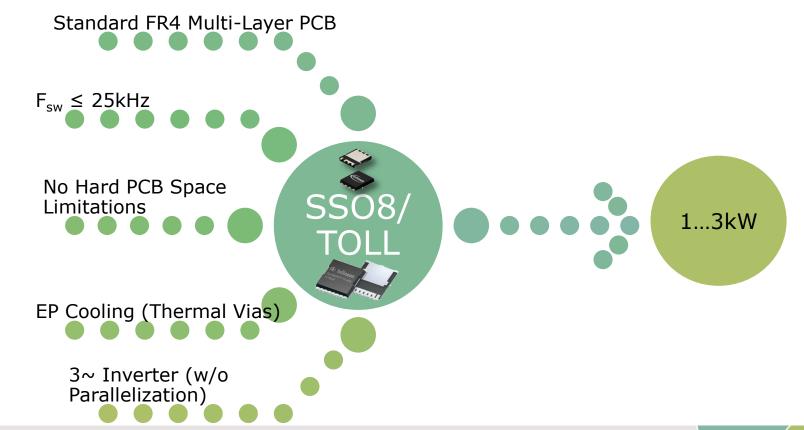

## Limitations of Leadless SMD Packages System Requirements

Copyright © Infineon Technologies AG 2017. All rights reserved.

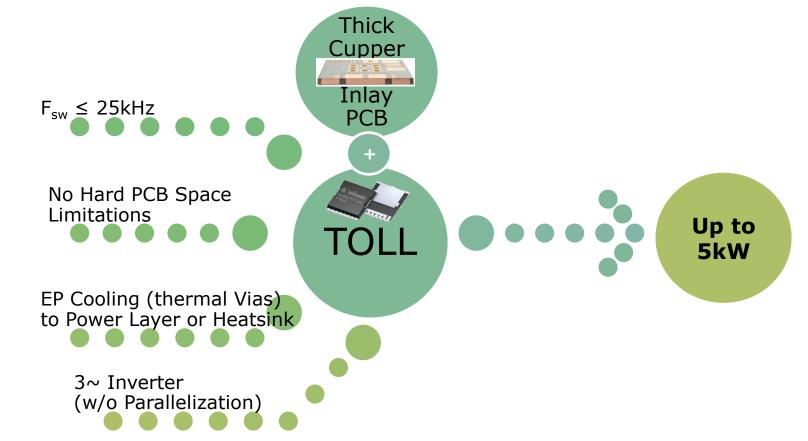

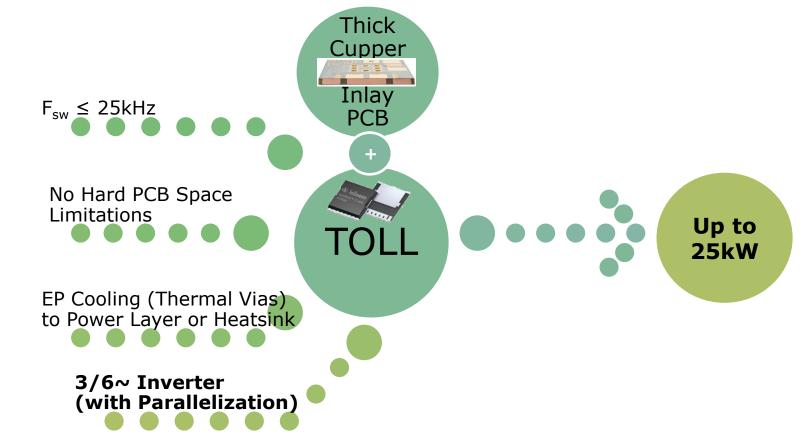

## Limitations of Leadless SMD Packages Increasing the Output Power with Thick Copper PCB

## Limitations of Leadless SMD packages Increasing the Output Power with Thick Copper PCB

## Leadless SMD MOSFETs High Power Inverters

> Electrification and Hybridization

## Leadless SMD Packages Advantages

#### Assembly

- > Optical Inspection

- Standard Soldering Process (e.g. Reflow)

## Quality

- > Fully AECQ qualified

- Proven IOL (Power Cycling) and TCoB (Temp Cycling) Reliability

# Market 2<sup>nd</sup> Source Strategy Multiple, Footprint > Compatible Alternatives available **PCB** Standard FR4 **Multiple Supplier**

Well Known Copper Technologies

## Limitations of Leadless SMD Packages Disadvantages

#### PCB

- > Increased PCB Temperature

- > Layout Inflexibility

- High Thermal Stress on Solder Mask (->reliability)

- Only applicable for Copper Substrate

#### Parallel Switching Performance

- Parameter Variation

- > Gate-Threshold Voltage,

- > Breakdown Voltage

## Cooling

- R<sub>thJunction-Ambient</sub> limited by Package

- Thick Copper Layer or Inlay

- > Bottom Side Cooling

#### Power

Limited by Bonding/Clipping (per device)

# Agenda

| 1 | High Power Inverters          |

|---|-------------------------------|

| 2 | Leadless SMD Packages         |

| 3 | Bare Dies and MOSFET Modules  |

| 4 | Innovative Packaging Concepts |

| 5 | Chip Embedding                |

| 6 | Summary and Outlook           |

Modules

Switching

**Reduced Stray**

on Design

Σ

>

>

## Bare Dies and MOSFET Modules Advantages

### **System Dimensions** Power Customized Chip Size Most Flexible Design Adaptive to All Circumstances **Temperature & Cooling** > Applicable for Inductance depending **HOT Environments** (up to 175°C) **Customized Cooling** >

**Approaches**

>

Homogeneous

Power Loss Distribution

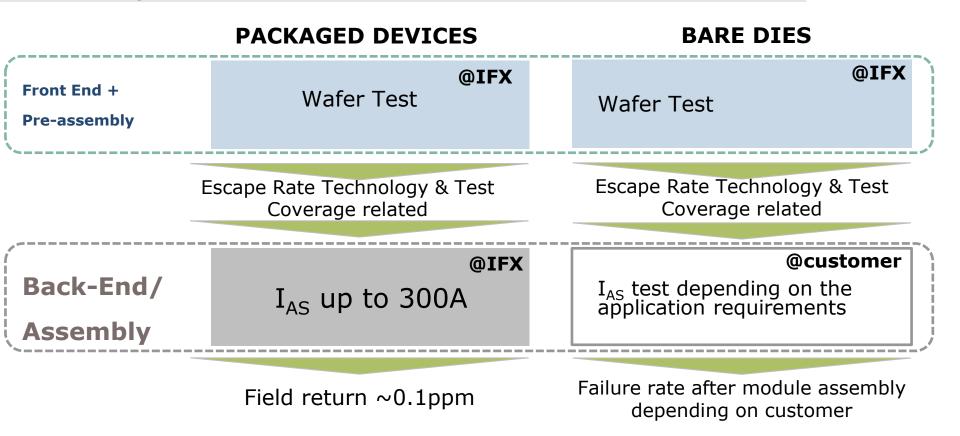

## Bare Dies and MOSFET Modules Reliability: PPM Rates

## Bare Dies and MOSFET Modules Disadvantages

#### Yield @ Customer

Yield Loss after Assembly @ Customer

#### Testing

- Avalanche Current Testing at Customer Required

- Need of Additional Module Stress Tests (e.g. Power & Temp Cycling)

#### Handling

- > Thin Wafer Technology

- Very sensitive to Cracks

- Strongly depending on Customer's Experience

#### Assembly

Customer is Responsible for entire Back-End-of-Line Process

# Agenda

| 1 | High Power Inverters          |

|---|-------------------------------|

| 2 | Leadless SMD Packages         |

| 3 | Bare Dies and MOSFET Modules  |

| 4 | Innovative Packaging Concepts |

| 5 | Chip Embedding                |

|   |                               |

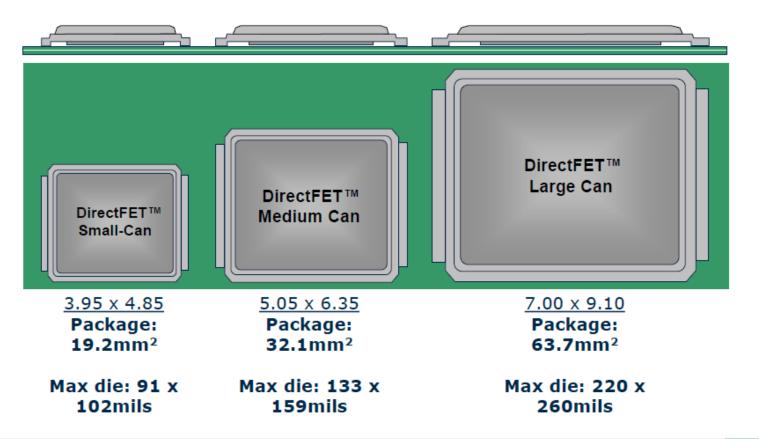

## Innovative Packaging Concepts DirectFET2/TOLG/Top Side Cooling

|                       | DirectFET2<br>(WDSON)                    | TOLG             |

|-----------------------|------------------------------------------|------------------|

|                       | (Ling)                                   |                  |

| Foot-Print            | 7x9                                      | 10x12mm          |

| I-Package             | 88A                                      | 300A             |

| Released              | Gen10.7<br>100V                          | OptiMOS™5<br>80V |

| R <sub>DSon</sub> BiC | 2.8mΩ                                    | 1.2mΩ            |

|                       | Dual Side                                | Bottom Side      |

| PCB/Cooling           | Bottom: FR4 Copper<br>Top: Water Cooling |                  |

#### Preliminary Information. Subject to change.

2017-10-12

# Innovative Packaging Concepts TOLG

|                       | DirectFET2<br>(WDSON)                    | TOLG                       |

|-----------------------|------------------------------------------|----------------------------|

|                       | (Ling)                                   |                            |

| Foot-Print            | 7x9                                      | 10x12mm                    |

| I-Package             | 88A                                      | 300A                       |

| Released              | Gen10.7<br>100V                          | OptiMOS™5<br>80V           |

| R <sub>DSon</sub> BiC | 2.8mΩ                                    | 1.2mΩ                      |

|                       | Dual Side                                | Bottom Side                |

| PCB/Cooling           | Bottom: FR4 Copper<br>Top: Water Cooling | Bottom:<br>FR4/Al-core IMS |

#### Preliminary Information. Subject to change.

2017-10-12

## TOLG Properties of Al-based IMS and Consequences

- infineon

- Cu (based Material for the Leadframe of the MOSFET), Al and FR4 have different Coefficients of Thermal Expansion:

- The Mismatch between Cu and Al-Core IMS will lead to higher Stress on the Solder Material, and reduce the Robustness of the System during Thermal Cycles, which may lead to Cracks within the Solder Material

- → Failure Mode: always Solder Joint Fatigue at the Corner Pins @ Gate/Source

- → TOLL is appropriate for FR4 Boards and Cu-Core IMS

# TCoB Performance of TOLL and TOLG on IMS (-40°C to 125°C):

## TOLG TOLL with Gullwing Geometry

Infineon investigated a Derivate of the TOLL (TOLL with Gullwing Geometry) to improve TCoB performance on Al-core IMS:

- > Results:

- On IMS: the TOLG performs much better than the TOLL under same Conditions

- Reason for better Performance is the Flexibility of the Gullwing Leads

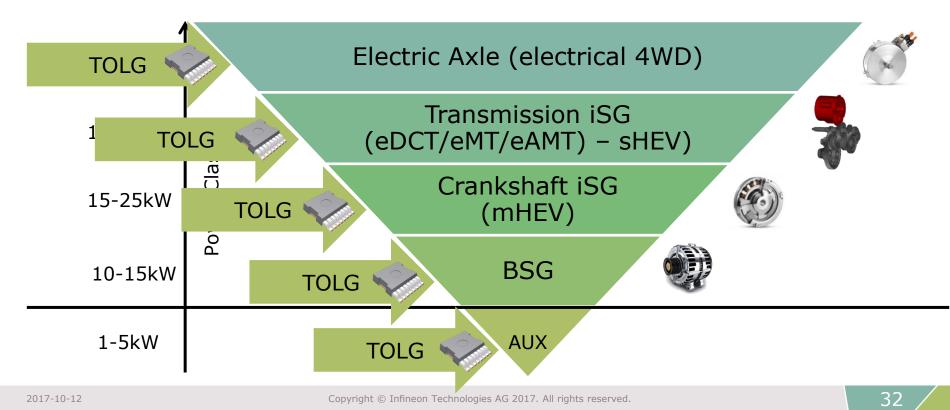

## TOLG High Power Inverters

> Electrification and Hybridization

## Innovative Packaging Concepts DirectFET2

|                       | DirectFET2<br>(WDSON)                    | TOLG             |

|-----------------------|------------------------------------------|------------------|

|                       | (Linger                                  |                  |

| Foot-Print            | 7x9mm                                    | 10x12mm          |

| I-Package             | 88A                                      | 300A             |

| Released              | Gen10.7<br>100V                          | OptiMOS™5<br>80V |

| R <sub>DSon</sub> BiC | 2.8mΩ                                    | 1.2mΩ            |

|                       | Dual Side                                | Bottom Side      |

| PCB/Cooling           | Bottom: FR4 Copper<br>Top: Water Cooling |                  |

#### Preliminary Information. Subject to change.

2017-10-12

## Innovative Packaging Concepts DirectFET2

Innovative Packaging Concepts DirectFET2

- > Allowing Double Side Cooling

- Top-Side: Heatsink / Water Cooling

200um die

thickness

175um SAC305

- Bottom-Side: Thermal Vias to Power Cu Layer

MSL1 capable epoxy die

attach

64um

dimples on

Copyright © Infineon Technologies AG 2017. All rights reserved.

Drain

Cu leadframe, 250um

thick material

Heatsink/Water Cooling

PCB

Drain

Source

DirectFET2 Applications

Copyright © Infineon Technologies AG 2017. All rights reserved.

DirectFET2 Advantages

### Switching

Lowest Stray Inductance in Class due to missing Bond Wires

### Quality

- Fully AECQ qualified

- Proven IOL (Power Cycling) and TCoB (Temp Cycling) Reliability

### Cooling

- Double Side Cooling

- Very low Top Side

R<sub>th</sub> enables Cooling via

CAN to Heatsink

### PCB

- Standard FR4

- Reduced PCB Temperature

### Limitations of DirectFET2 Disadvantages

### **PCB & Assembly**

- Increased PCB Temperature >

- Layout Inflexibility >

- Deviations of Body's Height: > No Homogeneous Placement of Thin Thermal Adhesive

### Parallel Switching Performance

- Parameter Variation

- Gate-Threshold Voltage

- Breakdown Voltage >

## Market > Unique No Footprint > **Compatible Alternatives Power Cycling** Bottle Neck : 5 Bottom-Side Solder Bumps (High Thermal Stress)

## Agenda

| 1 | High Power Inverters          |

|---|-------------------------------|

| 2 | Leadless SMD Packages         |

| 3 | Bare Dies and MOSFET Modules  |

| 4 | Innovative Packaging Concepts |

| 5 | Chip Embedding                |

| 6 | Summary and Outlook           |

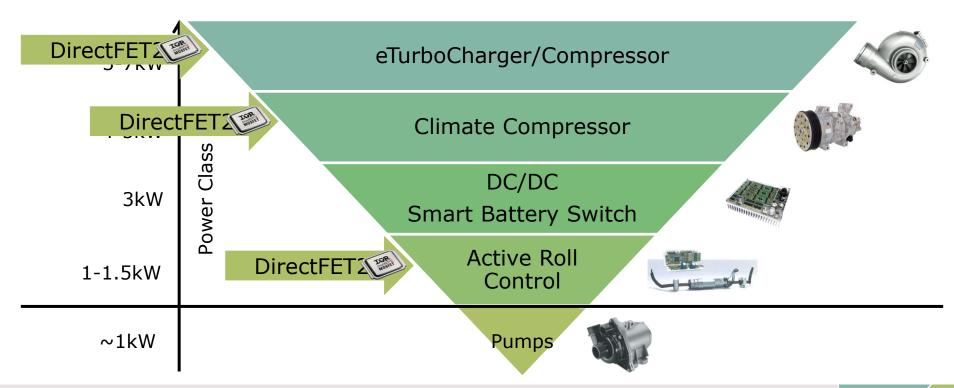

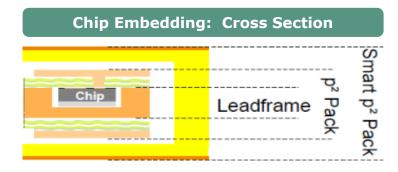

### Chip Embedding Process Flow

#### Chip Embedding: Increasing System Performance

| ≻       | Low Ohmic Conductivity  | +++ |

|---------|-------------------------|-----|

| $\succ$ | Low Inductive Switching | +++ |

| $\succ$ | System Cooling          | +++ |

| $\succ$ | System Miniaturization  | +++ |

| ≻       | System Assembly         | +++ |

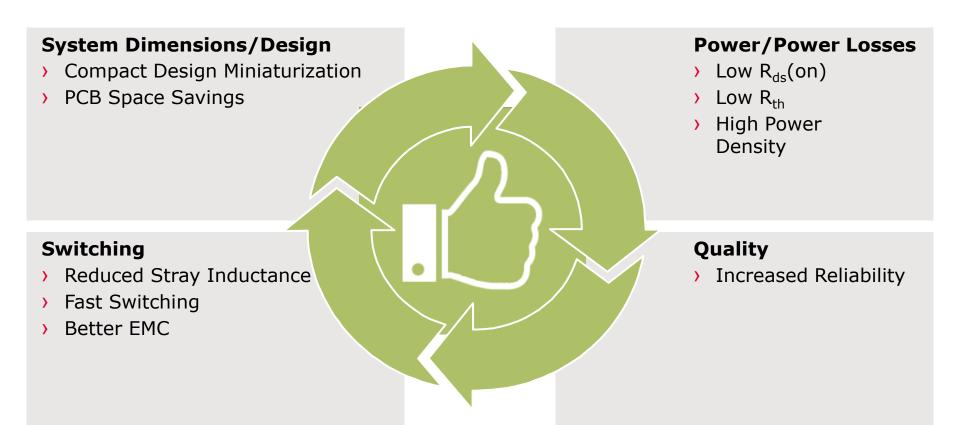

### Chip Embedding Advantages

#### 2017-10-12

Copyright © Infineon Technologies AG 2017. All rights reserved.

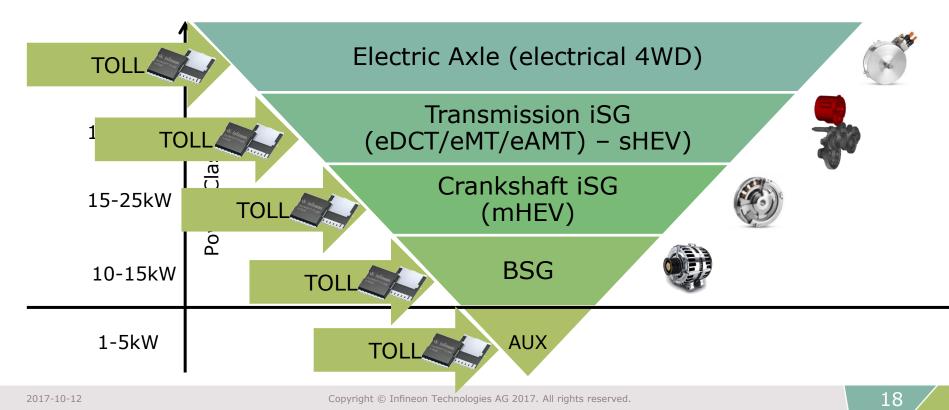

# High Power Inverters µHybridization

42

#### 2017-10-12

Copyright © Infineon Technologies AG 2017. All rights reserved.

## High Power Inverters Auxiliary Drives

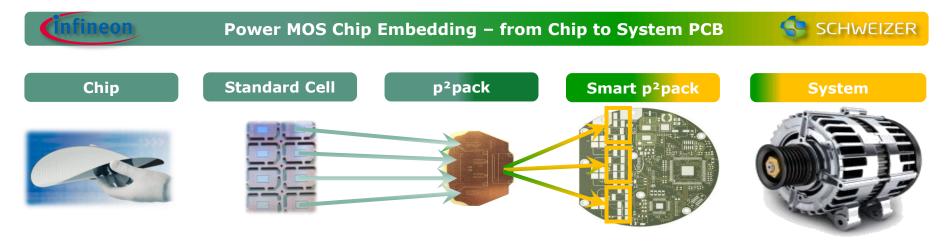

## Power MOS Chip-Embedding Potential System Improvements & Savings

Ceramic Board or Power PCB + Save Connectors and Logic PCB = become only one PCB Enhance Interconnects Better thermal & electrical Save Cooling Performance Reduction of Chip Size and / or **Save Semiconductor Costs** Lower Voltage Class Faster Switching possible Save Passives **Save EMC Measures** EMC Shielding with Cu-Layers Power stages are already insulated Save Insulator Save Room/Space constrains Miniaturization - Less Space "Money in Hybrid Cars" DC Link close to power stages Save System Costs

➔ Optimizing System Performance & System Costs

## Agenda

| 1 | High Power Inverters          |

|---|-------------------------------|

| 2 | Leadless SMD Packages         |

| 3 | Bare Dies and MOSFET Modules  |

| 4 | Innovative Packaging Concepts |

| 5 | Chip Embedding                |

| 6 | Summary and Outlook           |

|                                            | Air cooling (**) | External Water Cooling (***) |

|--------------------------------------------|------------------|------------------------------|

|                                            |                  | TOLL/TOLG on IMS             |

|                                            |                  | (105µmCu, 2mm Al)            |

|                                            |                  |                              |

| RthJH [K/W]                                |                  | 2                            |

| R <sub>thJH</sub> Improvement [%]          |                  | -                            |

| TJ,max [°C]                                |                  | 175                          |

| Ta,max [°C]                                |                  | 110                          |

| DT [K]                                     |                  | 65                           |

| R"pck" [mOhm]                              |                  | 0,16                         |

| R <sub>″pck″</sub> [%]                     |                  | -                            |

| RDSon,max25%C [mOhm]                       |                  | 1,5                          |

| R <sub>DSon,max"25%C</sub> Improvement [%] |                  | -                            |

| Ls [nH]                                    |                  | 2                            |

| L <sub>s</sub> Improvement [%]             |                  | -                            |

| Switching losses                           |                  | 30%                          |

| Max current ratings RMS [A]                |                  | 95                           |

| Current Improvement [%]                    |                  | -                            |

| (*) Concept - based on Simulatio           | n                | Reference:                   |

(\*\*) Low Budget Cooling

|                                            | Air cooling (**) |

|--------------------------------------------|------------------|

|                                            | DCB              |

|                                            | Wedge bonded     |

|                                            | 175µm Si         |

| RthJH [K/W]                                | 2                |

| R <sub>thJH</sub> Improvement [%]          | 0%               |

| TJ,max [°C]                                | 175              |

| Ta,max [°C]                                | 110              |

| DT [K]                                     | 65               |

| R"pck" [mOhm]                              | 0,5              |

| R <sub>"pck"</sub> [%]                     | 213%             |

| RDSon,max25%C [mOhm]                       | 1,84             |

| R <sub>DSon,max"25%C</sub> Improvement [%] | 23%              |

| Ls [nH]                                    | 5                |

| L <sub>s</sub> Improvement [%]             | 150%             |

| Switching losses                           | 40%              |

| Max current ratings RMS [A]                | 84               |

| Current Improvement [%]                    | -12%             |

| (*) Concept based on Cimula                |                  |

(\*) Concept - based on Simulation

(\*\*) Low Budget Cooling

|                                            | Air cooling (**) |              | External Water Coolin |

|--------------------------------------------|------------------|--------------|-----------------------|

|                                            | DCB              | DCB          | TOLL/TOLG on IMS      |

|                                            | Wedge bonded     | Wedge bonded |                       |

|                                            | 175µm Si         | 175µm Si     | (105µmCu, 2mm Al)     |

| RthJH [K/W]                                | 2                | 1            |                       |

| R <sub>thJH</sub> Improvement [%]          | 0%               | -50%         | -                     |

| TJ,max [°C]                                | 175              | 175          | 17                    |

| Ta,max [°C]                                | 110              | 110          | 110                   |

| DT [K]                                     | 65               | 65           | 65                    |

| R"pck" [mOhm]                              | 0,5              | 0,5          | 0,10                  |

| R <sub>"pck"</sub> [%]                     | 213%             | 213%         | -                     |

| RDSon,max25%C [mOhm]                       | 1,84             | 1,84         | 1,!                   |

| R <sub>DSon,max"25%C</sub> Improvement [%] | 23%              | 23%          | -                     |

| Ls [nH]                                    | 5                | 5            |                       |

| L <sub>s</sub> Improvement [%]             | 150%             | 150%         | -                     |

| Switching losses                           | 40%              | 40%          | 30%                   |

| Max current ratings RMS [A]                | 84               | 117          | 99                    |

| Current Improvement [%]                    | -12%             | 23%          | -                     |

|                                            |                  |              | Reference:            |

(\*) Concept - based on Simulation

(\*\*) Low Budget Cooling

|                                            | Air cooling (**) |              | External Water Cooling (*** |                   |

|--------------------------------------------|------------------|--------------|-----------------------------|-------------------|

|                                            | DCB              | DCB          | DCB (*)                     | TOLL/TOLG on IMS  |

|                                            | Wedge bonded     | Wedge bonded | SFS                         |                   |

|                                            | 175µm Si         | 175µm Si     | 70µm Si                     | (105µmCu, 2mm Al) |

| RthJH [K/W]                                | 2                | 1            | 0,9                         | 2                 |

| R <sub>thJH</sub> Improvement [%]          | 0%               | -50%         | -55%                        | -                 |

| TJ,max [°C]                                | 175              | 175          | 175                         | 175               |

| Ta,max [°C]                                | 110              | 110          | 110                         | 110               |

| DT [K]                                     | 65               | 65           | 65                          | 65                |

| R"pck" [mOhm]                              | 0,5              | 0,5          | 0,12                        | 0,16              |

| R <sub>"pck"</sub> [%]                     | 213%             | 213%         | -25%                        | -                 |

| RDSon,max25%C [mOhm]                       | 1,84             | 1,84         | 1,46                        | 1,5               |

| R <sub>DSon,max"25%C</sub> Improvement [%] | 23%              | 23%          | -3%                         | -                 |

| Ls [nH]                                    | 5                | 5            | 2                           | 2                 |

| L <sub>s</sub> Improvement [%]             | 150%             | 150%         | 0%                          | -                 |

| Switching losses                           | 40%              | 40%          | 30%                         | 30%               |

| Max current ratings RMS [A]                | 84               | 117          | 144                         | 95                |

| Current Improvement [%]                    | -12%             | 23%          | 52%                         | -                 |

| (*) Concept based on Simula                |                  |              |                             | Reference:        |

(\*) Concept - based on Simulation

(\*\*) Low Budget Cooling

|                                            | Air cooling (**)         | Air cooling (**)         |                | External Water Cooling (***) |        |  |

|--------------------------------------------|--------------------------|--------------------------|----------------|------------------------------|--------|--|

|                                            | DCB                      | DCB                      | DCB (*)        | TOLL/TOLG on IMS             |        |  |

|                                            | Wedge bonded<br>175µm Si | Wedge bonded<br>175µm Si | SFS<br>70µm Si | (105µmCu, 2mm Al)            | CE (*) |  |

| RthJH [K/W]                                | 2                        | 1                        | 0,9            | 2                            | 1      |  |

| R <sub>thJH</sub> Improvement [%]          | 0%                       | -50%                     | -55%           | -                            | -50%   |  |

| TJ,max [°C]                                | 175                      | 175                      | 175            | 175                          | 175    |  |

| Ta,max [°C]                                | 110                      | 110                      | 110            | 110                          | 110    |  |

| DT [K]                                     | 65                       | 65                       | 65             | 65                           | 65     |  |

| R"pck" [mOhm]                              | 0,5                      | 0,5                      | 0,12           | 0,16                         | 0,1    |  |

| R <sub>"pck"</sub> [%]                     | 213%                     | 213%                     | -25%           | -                            | -38%   |  |

| RDSon,max25%C [mOhm]                       | 1,84                     | 1,84                     | 1,46           | 1,5                          | 1,44   |  |

| R <sub>DSon,max"25%C</sub> Improvement [%] | 23%                      | 23%                      | -3%            | -                            | -4%    |  |

| Ls [nH]                                    | 5                        | 5                        | 2              | 2                            | "1"    |  |

| L <sub>s</sub> Improvement [%]             | 150%                     | 150%                     | 0%             | -                            | -50%   |  |

| Switching losses                           | 40%                      | 40%                      | 30%            | 30%                          | 20%    |  |

| Max current ratings RMS [A]                | 84                       | 117                      | 144            | 95                           | 144    |  |

| Current Improvement [%]                    | -12%                     | 23%                      | 52%            | -                            | 52%    |  |

| (*) Concept based on Simula                | Reference:               |                          |                |                              |        |  |

(\*) Concept - based on Simulation

(\*\*) Low Budget Cooling

(\*\*\*) High End Cooling

2017-10-12

|                                            | Air cooling (**) | External Water Cooling (***) |         |                          |                         |      |

|--------------------------------------------|------------------|------------------------------|---------|--------------------------|-------------------------|------|

|                                            | DCB              | DCB                          | DCB (*) | TOLL/TOLG on IMS         | /TOLG on IMS            |      |

|                                            | Wedge bonded     | Wedge bonded                 | SFS     | (105µmCu, 2mm Al) CE (*) | Top Side<br>Cooling (*) |      |

|                                            | 175µm Si         | 175µm Si                     | 70µm Si |                          |                         |      |

| RthJH [K/W]                                | 2                | 1                            | 0,9     | 2                        | 1                       | 1,6  |

| R <sub>thJH</sub> Improvement [%]          | 0%               | -50%                         | -55%    | -                        | -50%                    | -20% |

| TJ,max [°C]                                | 175              | 175                          | 175     | 175                      | 175                     | 175  |

| Ta,max [°C]                                | 110              | 110                          | 110     | 110                      | 110                     | 110  |

| DT [K]                                     | 65               | 65                           | 65      | 65                       | 65                      | 65   |

| R"pck" [mOhm]                              | 0,5              | 0,5                          | 0,12    | 0,16                     | 0,1                     | 0,16 |

| R <sub>″pck″</sub> [%]                     | 213%             | 213%                         | -25%    | -                        | -38%                    | 0%   |

| RDSon,max25%C [mOhm]                       | 1,84             | 1,84                         | 1,46    | 1,5                      | 1,44                    | 1,5  |

| R <sub>DSon,max"25%C</sub> Improvement [%] | 23%              | 23%                          | -3%     | -                        | -4%                     | 0%   |

| Ls [nH]                                    | 5                | 5                            | 2       | 2                        | "1"                     | 2    |

| L <sub>s</sub> Improvement [%]             | 150%             | 150%                         | 0%      | -                        | -50%                    | 0%   |

| Switching losses                           | 40%              | 40%                          | 30%     | 30%                      | 20%                     | 30%  |

| Max current ratings RMS [A]                | 84               | 117                          | 144     | 95                       | 144                     | 107  |

| Current Improvement [%]                    | -12%             | 23%                          | 52%     | -                        | 52%                     | 13%  |

| (*) Concert based on Circula               |                  |                              |         | Reference:               |                         |      |

(\*) Concept - based on Simulation

(\*\*) Low Budget Cooling

(\*\*\*) High End Cooling

2017-10-12

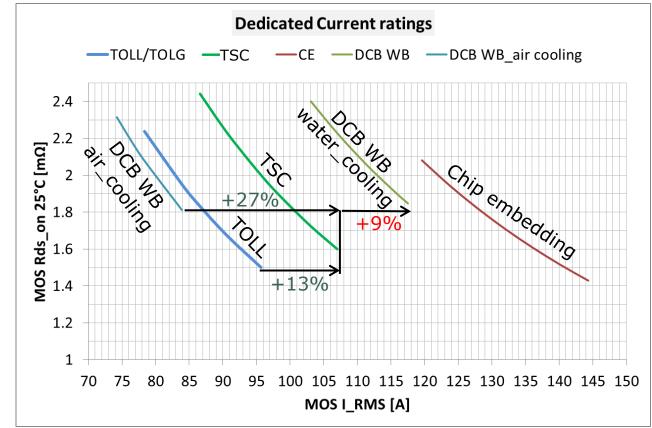

## Current Ratings Distribution According to Packages and Cooling Concept

100V MOS R<sub>ds</sub>(on)@25C Vs Id\_RMS (Application Verification)

### Summary Comparison of MOSFET Solutions

| TOLL<br>TOLG                                     | DirectFET2                                                                                                                | Bare Die<br>(Modules)                                                                                                                                                                                                                                                                      | Chip Embedding<br>(P <sup>2</sup> PAK)                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SFET5<br>++                                      | Gen10.7<br>+                                                                                                              | SFET4<br>+                                                                                                                                                                                                                                                                                 | SFET5<br>++                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.5mOhm<br>(100V)<br>1.2mOhm (80V)               | 2.8mOhm (100V)<br>1.8mOhm (75V)                                                                                           | 1.9mOhm (100V)<br>0.66mOhm (80V)                                                                                                                                                                                                                                                           | flexible                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4x 6 MOSFETs =<br>24<br>2880mm <sup>2</sup><br>0 | 4x 6 MOSFETs =<br>24<br>1560mm <sup>2</sup><br>+                                                                          | 30.24mm <sup>2</sup> /die * 2<br>(in parallel) * 6 =<br>362.88mm <sup>2</sup> (die<br>space) + module                                                                                                                                                                                      | 30mm <sup>2</sup> / chip<br>P <sup>2</sup> PAK can be<br>integrated space-<br>neutral<br>(embedding)<br>++                                                                                                                                                                                                                                                                                                                                                                                       |

| +                                                | +                                                                                                                         | -                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 300A                                             | 124A                                                                                                                      | 272A                                                                                                                                                                                                                                                                                       | 300A<br>+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                  | <b>TOLG</b><br>SFET5<br>++<br>1.5mOhm<br>(100V)<br>1.2mOhm (80V)<br>4x 6 MOSFETs =<br>24<br>2880mm <sup>2</sup><br>0<br>+ | TOLG       Gen10.7         ++       Gen10.7         1.5mOhm       2.8mOhm (100V)         1.5mOhm (80V)       1.8mOhm (75V)         1.2mOhm (80V)       4x 6 MOSFETs =         24       4x 6 MOSFETs =         24       1560mm²         0       +         +       +         300A       124A | TOLG       (Modules)         SFET5       Gen10.7       SFET4         ++       +       1.9mOhm (100V)         1.5mOhm       2.8mOhm (100V)       1.9mOhm (100V)         (100V)       1.8mOhm (75V)       0.66mOhm (80V)         1.2mOhm (80V)       4x 6 MOSFETs =       30.24mm²/die * 2         4x 6 MOSFETs =       4x 6 MOSFETs =       30.24mm²/die * 2         24       1560mm²       362.88mm² (die         0       +       -         +       +       -         300A       124A       272A |

### Summary Comparison of MOSFET Solutions

|                                                         | TOLL<br>TOLG | DirectFET2 | Bare Die<br>(Modules) | Chip Embedding<br>(P <sup>2</sup> PAK) |

|---------------------------------------------------------|--------------|------------|-----------------------|----------------------------------------|

| Customization:<br>differentiation to the<br>competition | -            | +          | ++                    | ++                                     |

| Layout flexibility                                      | 0            | 0          | ++                    | ++                                     |

| Handling                                                | +            | 0          | -                     | 0                                      |

| Portability from one gen to the next                    | ++           | 0          | -                     | ++ (TIER1)                             |

Part of your life. Part of tomorrow.